Hard built-in pre-adders can be used when implementing symmetric filters to. VHDL Finite Impulse Response FIR Filter Share Finite Impulse Response FIR Filter The VHDL code presented in this model will show you how to describe a typical reference model in VHDL.

A Low Pass Fir Filter For Ecg Denoising In Vhdl Fpga4student Com

DIGITAL FILTER DESIGN 78 VHDL CODES FOR FIR FILTERS USING BIT-PARALLEL ARITHMETIC VHDL Code for 4-BIT COUNTER entity counter_4_bit is Port clk.

. Here below is reported the VHDL code for the FIR filter design of figure 2. Vhdl code for a 4 tap fir filter finite impulse response fir filters are one of the two main type of filters available for signal processing. Video Lecture on an FPGA-Implementation of an FIR-Filter 2 of 4Project Homepagehttpwwwh-brsdefpga-vision-labSource Code available athttpsgithub.

Vhdl Code For Fir Filter. A finite impulse response FIR filter is a type of a discrete-time filter. Firs Abies are a genus of 4855 species of evergreen conifers in the family Pinaceae.

Reconfigurable fir filter vhdl code. VHDL code for the FIR filter is fully presented. In the VHDL we set the FIR coefficient as a constant value.

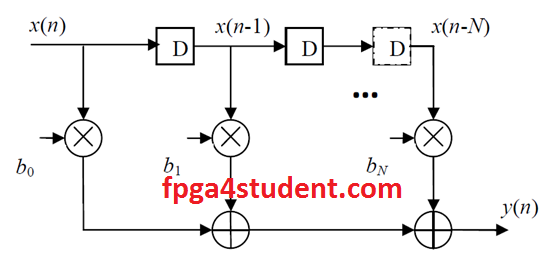

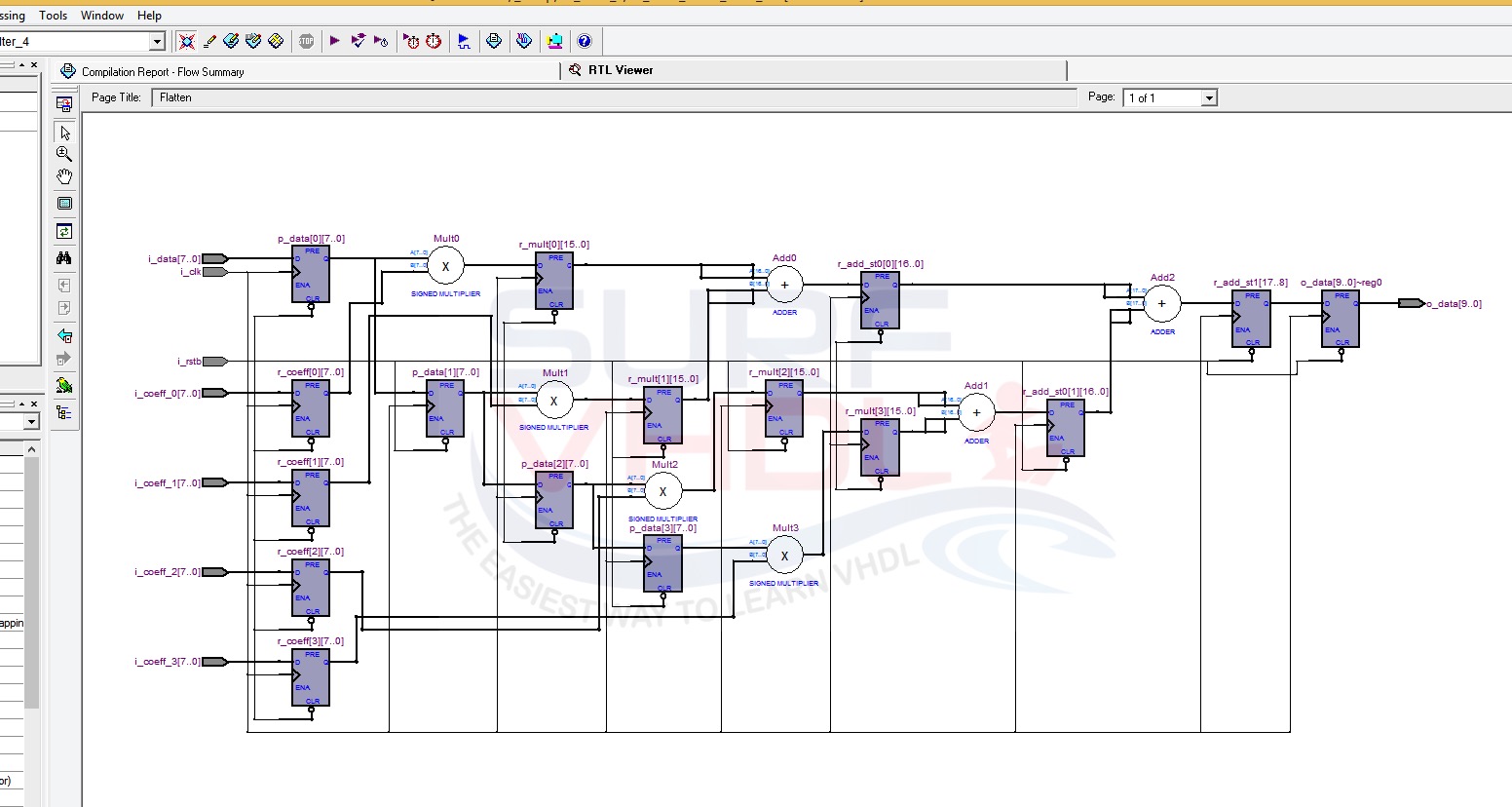

From the simulation in Figure 7 the DELTA response of the FIR filter in the bottom view reports the filter coefficient divided by 2. RTL-VHDL-Code Block diagram Algorithm High-Level System Diagram Context of the design Inputs and Outputs Throughputrates Algorithmic requirementsy k bi x k i N Algorithm Description Mathematical Description i 0 Performance Criteria x k y k. This paper mainly describes the design and simulation of FIR filter which is based on FPGA Xilinx tools and VHDL.

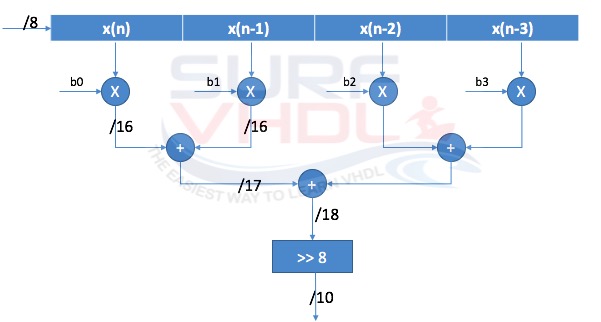

This is a 4 tap filter. The simplest low pass FIR filter you can try is y n x n x n-1. The impulse response the filters response to a Kronecker delta input is finite.

Nonresinous wood of a fir tree. In IOinput_vectorstxt put the input integer you want to test. An evergreen coniferous tree with upright cones and flat needle-shaped leaves.

Below is a very simple block diagram of the hardware you want to implement. Vhdl code for fir filter design. Summer is in the corner and it will almost always be One of the more awaited seasons of your year.

By using these tools the time required to get the desired results becomes very less. Logic for simple 15-tap FIR to be written in Verilog or VHDL Notice how the valid and ready signals set the enable value for the input circular buffer and the multiply stage of the FIR and each of the registers that the data or coefficients pass through are declared as signed. Classics design the VHDL source code downloads classics the design to i.

Check IOoutput_resultstxt for the result. That means the order of the filter is 4 and so it has 4 coefficients. Alteras 28-nm DSP architecture includes a host of features for optimizing FIR filter implementations.

In order to calculate the filter coefficients the first step is to specify the cutoff frequency the. FIR Filter Where to start. You can implement this quite easily in VHDL.

FIR module Verilog code. Using the MATLAB software we design such core modules as CIC filter HB filter and FIR filter of the digital down converter. 1 Points Download Earn points.

Usbdriverzip Basic programing method for USB driver worth reading. Source Code reconfigurable fir filter vhdl code. 0 Low pass 1 High Pass.

This is a 4 tap filter. Well use a 32-tap FIR filter as an example. They are found through much of North and Central America Europe Asia and North Africa occurring in mountains over most of the range.

FIR filter coefficients design has been performed using the MATLAB. The VHDL code for the FIR filter is simulated and verified by comparing the simulated results in Modelsim with the correct results generated from Matlab. For a discussion of the advantages of reference models please refer to our Tips page.

That means the order of the filter is 4 and so it has 4 coefficients. The VHDL code implements a low pass FIR filter with 4 taps 8-bit input 8-bit coefficient. The filter designer code looks the following way.

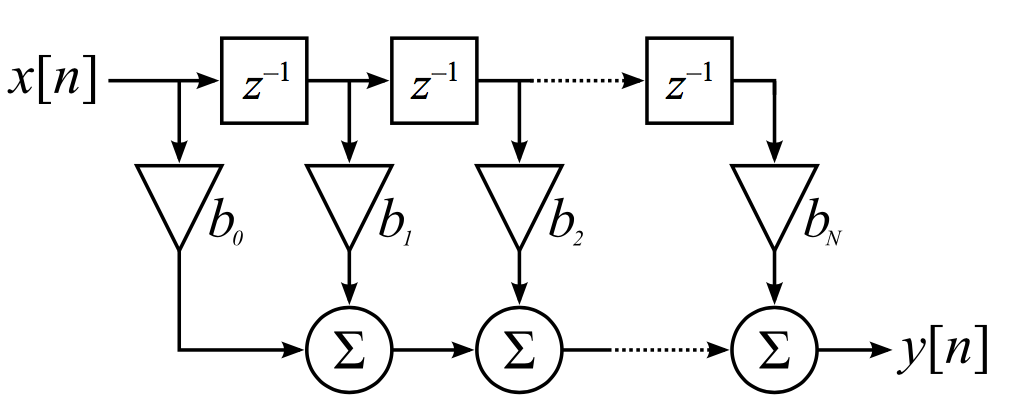

An implementation of a FIR filter in particular using the transposed form. This is an fir filter implementation code for a reconfigurable fir filter design coded in vhdl language. Timescale 1ns 1ps module FIR input clk.

Its the ideal time for you to do this easy still pretty hunting nails. You can say I have coded the exact block diagram available in the paper Figure 2. The higher the value of N is the more complex the filter will be.

Inout STD_LOGIC_VECTOR 4 downto 1. Architecture Behavioral of counter_4_bit is component. For writing the code in VHDL I have referred to the paper VHDL generation of optimized FIR filters.

File list Click the file name to view code. VHDL VHDL code for low pass FIR filter FIR filter ECG Denoising in VHDL VHDL code for ECG Denosing FIR Filter PYNQ Python productivity for Zynq Community May 8th 2018 - PYNQ is an open source project from Xilinx that makes it easy to design embedded systems with Xilinx Zynq All Programmab vhdl tutorial learn by example may 8th 2018. The structure of FIR filter has been implemented on a FPGA kit.

For writing the code in Verilog I have referred to the paper VHDL generation of optimized FIR filters. You can say I have coded the exact block diagram available in the paper Figure 2. Run the testbench on ModelSim.

The VHDL code of the filter test bench implements straight forward the architecture of Figure 6. Modify the file VHDLfir_tbvhdl modifying the path for data io. 15 Figure 8 Test bench simulation of 30 order FIR filter 16.

According to the formula you need the current and previous ADC samples in order to get the appropriate output. Transposed FIR Filter where N is the number of filter taps-1 ie. Inout STD_LOGIC_VECTOR 4 downto 1.

Function FilterDesigner CutOffFreq20change in Hz max 12 of the sample frequency SampleRate100Sample Rate Bandwidth of the filter BW002Change MakeHighPass0. Figure 2 Transposed Form Of FIR Filter 09 Figure 3 Top level schema of the FIR filter 11 Figure 4 Xilinx 142 report of the filter design 13 Figure 5 VHDL Top level RTL Schema1 14 Figure 6 VHDL Top level RTL Schema2 14 Figure 7 Xilinx 142 full schematic of FIR order 30 filter. Sample ECG inputs are provided in inputtxt files the VHDL filter code reads those ECG files apply digital filtering and write the results into outputtxt files for verification.

FIR Filter Design in Arria VCyclone V DSP Block Using VHDL Inferring.

Fpga Code Example For Fir Iir Filters In Vhdl Electrical Engineering Stack Exchange

How To Implement Fir Filter In Vhdl Surf Vhdl

Fir Filter Vhdl Logic Engineering And Component Solution Forum Techforum Digi Key

Pdf Vhdl Generation Of Optimized Fir Filters Semantic Scholar

A Low Pass Fir Filter For Ecg Denoising In Vhdl Fpga4student Com

Fpga Fir Filter Circuit Architecture And Vhdl Design Youtube

0 comments

Post a Comment